EEE3473: Digital System Assignment, UPNM, Malaysia Design a 4-bit BCD adder that will add two BCD numbers and produce the sum in BCD format. If the sum of two numbers

| University | Universiti Pertahanan Nasional Malaysia (UPNM) |

| Subject | EEE3473: Digital System |

Question 1

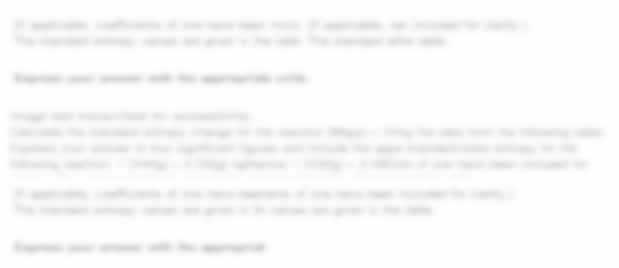

Design a 4-bit BCD adder that will add two BCD numbers and produce the sum in BCD format. If the sum of two numbers is less or equal to 9, then the value of the BCD sum is the same, otherwise, we need to add 6 (01102) to the sum. Figure 2 can be used as a guide. Draw a waveform to ensure the correctness of your design by showing all possibilities required.

Question 2

Design a sequential traffic light controller for the intersection of Jalan_A and Jalan_B. Each street has traffic sensors that detect the presence of vehicles approaching or stopping at intersections.

S_A=1 means a vehicle is approaching Jalan_A.

S_B=1 means a vehicle is approaching Jalan_B.

There are 3 outputs of each street Red_A, Yellow_A and Green_A, Red_B, Yellow_B, and Green_B.

Condition: “Jalan_A” is a main street and has a green light for at least 50s, after 50s if there is a car approaches “Jalan_B”, the light changes to yellow and then red, and “Jalan_B” has a green light for 50s.

At the end of the 50s, the light changed back unless there is a car on “Jalan_B” and none on “Jalan_A”. Start your design with FSM with all possibilities.

Write the Verilog code and waveform of your design.

Question 3

Design a simple Scoreboard which can display scores from 0 to 99. The input of the system should consist of a reset signal and control signals to increment or decrement the score.

The condition:

- The two-digit decimal count gets incremented by 1 if the increment signal is true and is decremented by 1 if the decremented signal is true.

- If increment and decrement are true simultaneously, no action occurs.

- The current count is displayed on 7-segment displays. In order to prevent accidental erasure, the reset button must be pressed for five consecutive cycles in order to erase the scoreboard. The scoreboard should allow down counts to correct a mistake.

Question 4

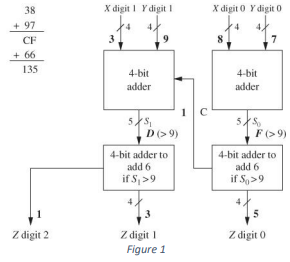

Design a 4-bit array multiplier using combinational logic as shown in figure 1.

Develop a waveform to show that your design is correct by adding all the possibilities.

Download your program into FPGA, and set your input as switch and output in LED seven segment.

Question 5

Develop a synchronous 3-bit up/down counter with Gray Code sequence using D- flip flop. The counter should count up when an 𝑈𝑃/𝐷𝑂𝑊𝑁 ̅̅̅̅̅̅̅̅̅ control input is 1 and count down when the control input is 0. Simulate its waveform to ensure the correctness of your design by showing all possibilities required.

Question 6

Use the RTL design process to create an alarm system that sets a single-bit output alarm to 1 when the average temperature of four consecutive samples meets or exceeds a user-defined threshold value. A 32-bit unsigned input CT indicates the current temperature, and a 32-bit unsigned input WT indicates the warning threshold. Samples should be taken every 5 clock cycles. A single-bit input clr when 1 disables the alarm and the sampling process. Start by capturing the desired system behavior as an HLSM, and then convert it to a controller/datapath. Write your Verilog code and download your program into FPGA. Set LED as your alarm indicator.

Get Help By Expert

If you're struggling with your homework and need a helping hand, Assignmenthelper.my is here to help. We offer comprehensive online homework help for students of all levels, from elementary school to university. Our experienced writers are experts in their fields and are available 24/7 to answer any questions you may have. With our assignment writing experts, you can rest easy knowing that your homework is in good hands. Try us out today and see the difference we can make!

Recent Solved Questions

- TCP1101: In this assignment, you will implement an assembly language interpreter that will run assembly language: Programming Fundamentals Assignment, UM, Malaysia

- GHZM 3063: Tourist Behaviour Assignment, UUM, Malaysia Students are required to design of either a transit centre

- NBHS1112: Describe the pathophysiology of Type II Diabetes Mellitus with links to Madam Suba’s case: biochemistry Assignment, OUM, Malaysia

- BBUN2103: BUSINESS LAW Assignment, OUM, Malaysia Evaluate the circumstances that occur prior to the formation of a contract that may impair the validity of the contract.

- CHE5884: Process modelling and optimization’s Case Study, MUM, Malaysia Calculate the hourly feed rate of the feedstock for the plant to produce the product assigned to your group

- Barriers to E-Invoicing in Malaysia: An Analysis of Technological and Regulatory Challenges

- Software Engineering Assignment, UOM, Malaysia Software reuse is a significant software engineering research field as well as a popular practice area in the industry

- Programming Paradigms Assignment, UiTM, Malaysia Form a group of a maximum of three (3) members and suggest a case study of any possible realistic scenario

- CSC508: Data Structure Assignment, UiTM, Malaysia Define your own Binary Search Tree (BST) data structure using Linked List

- You are planning for your financial retirement. You want to retire at 60. You plan to have an endowment fund that will give you a monthly income of RM 10,000 per month after retirement: Financial Management Assignment, UTP, Malaysia