EEE40002: Integrated Circuit Design Assignment, SUT, Malaysia Ability to evaluate the CMOS transistor characteristics and Conduct investigations of complex problems using research-based knowledge

| University | Swinburne University of Technology (SUT) |

| Subject | EEE40002: Integrated Circuit Design |

This assignment covers:

Ability to evaluate the CMOS transistor characteristics. Conduct investigations of complex problems using research-based knowledge (WK8) and research methods including design of experiments, analysis, interpretation of data, and synthesis of the information to provide valid conclusions.

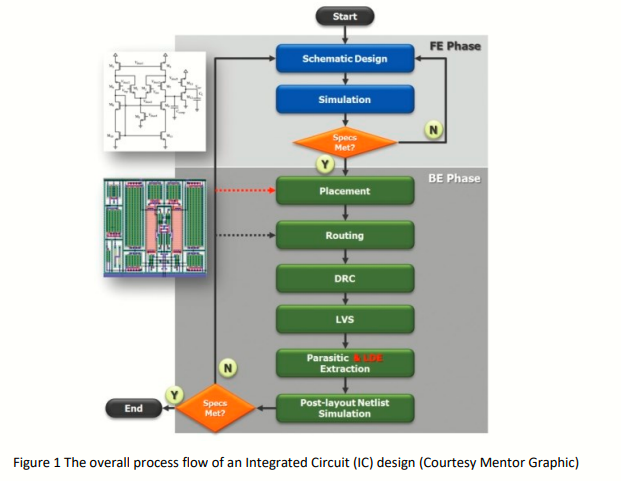

Figure 1 shows the overall process flow of an Integrated Circuit (IC) design.

SULIT

The operation begins with Front End Phase by creating the transistor-level schematic design based on the design specifications, before proceeding with the simulation step. In this simulation step, the test benches are required to verify the functionality of the design.

Next, the operation continues with Back End Phase by designing the layout based on the schematic design. Several steps are involved in this layout design phase such as Pre-layout design which includes Placement and Routing steps. Layout designers can always try different device placements and examine

the impact of any specific configuration of device placement on the original specification. Then, the process continues with DRC (Design Rule Check) and LVS (Layout Versus Schematic) steps. A successful DRC ensures that the layout conforms to the rules designed for faultless fabrication, while the successful LVS ensures that the layout connectivity of the physical design matches the schematic design.

Students in NMJ216043 was exposed to all the design process mentioned earlier. However, to achieve a successful post-layout design that meets all the specifications, important tasks like parasitic extraction is required. Students should be aware that the behavior of the layout design is extremely sensitive to the layout-induced parasitics such as inductance, resistance, and capacitance. Parasitics not only influence the layout performance but often render it non-functional. Hence, it is essential to consider the effect of parasitics in the design process. In conclusion, the major purpose of parasitic extraction is to create an accurate layout of a circuit, so that the simulations can emulate the actual circuit responses.

Get Help By Expert

Experience top-notch assistance for your Integrated Circuit Design assignment at Swinburne University of Technology. Explore Assignment Helper My, your dedicated partner for academic success. Our Malaysia-based online assignment helpers bring comprehensive insights and guidance to ensure your project's excellence. You also acquire our professionals for the best Online Exam Help.

Recent Solved Questions

- BMK311: Product Management Assignment, WOU, Malaysia Smart Home Technology was introduced in the early 2000s. Everyone in the world began talking about the Internet of Things

- PBD10202: ENGLISH II Essay, IIUM, Malaysia Steph was looking at Instagram there were blessed yoga photos and Sunday Breakfast pictures

- Business Ethics Assignment, CU, Malaysia Offering a bribe is wrong because it is an inducement to act dishonestly, disregard one’s duties, and betray a trust

- Curriculum Development Dissertation, UKM, Malaysia Curricula are defined at various levels, the state and classroom levels being the most well-known

- Food Science and Technology Assignment, UMS, Malaysia A tool to estimate food intake – individual/group. The food Composition Table for the USA has been published in 1981

- Auditing Assignment, MUS, Malaysia Discuss the importance and types of audits in an organization and Suggest the possible issues related to the financial statement

- To examine the teachers’ perceptions of the school principal’s leadership qualities: Educational Leadership, Report, UIU Malaysia

- ABKK1103: Introduction to Political Science Assignment, OUM, Malaysia There are many definitions related to politics. One of the most famous definitions of politics is by Harold Lasswell

- Marine science Thesis Proposal, UTM, Malaysia Fill a knowledge gap in comparing filter algorithms for classifying marine objects from UAV data

- Final Year Project Report malaysia To examine the two-way inflation-growth nexus across CPI sectors of Malaysia